SAN JOSE, Calif., April 20, 2021 /PRNewswire/ — Movellus, Inc. today announced its Maestro™ Intelligent Clock Network platform that intelligently orchestrates clock distribution in SoC designs. The platform provides critical clocking capabilities that address complex clock distribution requirements in modern SoCs, including AI applications in the cloud and at the edge. Maestro clocking solutions dramatically improve the entire chip’s power, performance, and area in a wide variety of markets.

Influencing every aspect of the system from timing closure to peak power demand, and from chip architecture to layout, the clock is one of the most complex signals in an SoC. Designs of all sizes and technology nodes experience SoC-level clock distribution challenges. On-chip variation (OCV), jitter, clock skews, peak switching current, switching noise, all increase with advanced process scaling. Today, clocking challenges are addressed by overdesigning the system. This creates further costs including up to 30% to 50% overhead of the SoC power and area. Furthermore, these designs end up limiting maximum clock frequency and consequently limit performance.

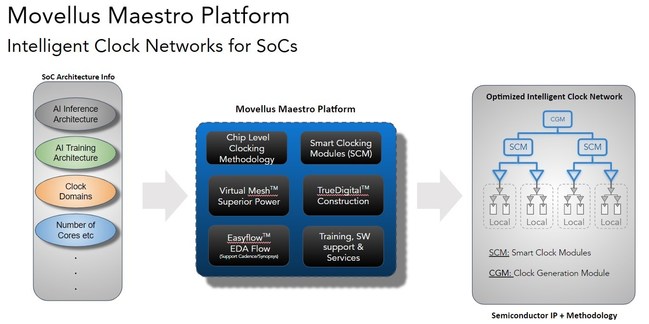

The Maestro platform automates the development of robust clock network solutions with powerful new capabilities. It combines a clock architecture, software automation, and application-optimized IP to solve common clock distribution challenges. Maestro is the only platform that provides end-to-end all-digital clocking network solutions, which offer better power, performance and area (PPA) and superior operating characteristics compared to traditional solutions. Additionally, they can scale to high-performance multi- GHz frequencies while occupying only a small footprint.

“Given the big impact clock distribution has on power, performance, and area in SoC designs, it hasn’t received the attention it deserves,” said Linley Gwennap, principal analyst at The Linley Group. “Movellus’ innovative solution reduces the complexity and risks inherent in today’s clock networks, including block and SoC timing closure and full chip gate-level simulation. It enables designers to recover up to 30% of the SoC’s power and performance through its pioneering smart clock modules that reduce the effect of on-chip variation and skew.”

“The complexity of today’s SoC designs, especially with the emergence of new AI chip architectures, is mind boggling. We see large scale designs with thousands of processors on a chip. We see IoT designs with nanowatt power requirements,” said Mo Faisal, President and CEO of Movellus. “System designers want to do things today that, quite frankly, would not be possible using traditional clock distribution solutions. Customers are very excited by the new capabilities intelligent clock networks bring. With the diversity of new and emerging architectures, there is a genuine and growing market need for them.”

Maestro incorporates Movellus’ TrueDigital™ construction including Clock Generator Modules (CGM), Smart Clock Modules (SCM), and Phase Shift Modules (PSM). CGMs are used for a variety of functions including clock generation and improved signal quality along the clock path. SCMs automatically sense and compensate for skew in the SoC clock path during runtime. PSMs reduce peak power and reduce voltage noise thereby relaxing voltage margins.

Another unique feature of Maestro is the ability to create a virtual mesh which can be thought of as a “network-on-chip (NoC) for the clock”. The virtual mesh can sense and compensate for on-chip variation and inter-block interactions globally. It enables automatic self-regulation of clocking throughout the SoC. Maestro enables highly efficient ultra-low power operation and supports high frequency multi-GHz performance. It eliminates the need to overdesign the system to compensate for on-chip variation or skew.

Movellus offers three reference configurations of its Maestro Intelligent Clock Network platform to address specific requirements based on the complexity of the application: Maestro AI, Maestro Cloud, and Maestro Phases. All use TrueDigital construction to generate RTL code that precisely meets application specifications. Their fully synthesizable architectures enable rapid RTL-to-GDS implementation and optimization. Maestro is designed to work seamlessly with existing digital tools and methodologies to reduce design complexity and significantly improve development time.

About Movellus

Movellus solves SoC-level clock distribution challenges in high performance and ultra low power chips. The company’s flagship platform, Maestro™ is an Intelligent clock network platform that delivers chip-level architectural innovations to improve SoC performance while reducing power consumption. All-digital, fully synthesizable clocking solutions achieve quantum leaps in energy efficiency. This accelerates the move to carbon-neutral data centers and enables ultra-low voltage operation for AI, IoT devices, and radiation hardened applications. Founded in 2014, Movellus is headquartered in San Jose, California. Visit us at www.movellus.com.

Media contact:

Pauline Shulman

307949@email4pr.com

415-707-9050

SOURCE Movellus